## 2.8 アウトプットコンペア機能による任意の位相差のパルス出力

アウトプットコンペア機能による任意の 使用機能 タイマW: アウトプットコンペア機能 <u>位相差のパルス出力</u>

仕様

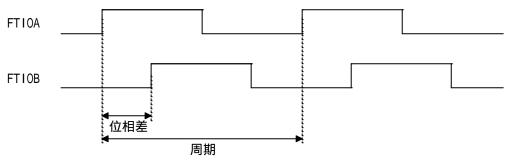

- (1)図1に示すように、タイマWアウトプットコンペア機能を使用して、デューティ50%のパルスを任意 の位相差で出力させます。

- (2)FTIOA出力端子およびFTIOB出力端子より、任意の位相差のパルスを出力します。

- (3) パルスの周期は、ジェネラルレジスタA(GRA)により設定します。

- (4) FTIOA、FTIOB端子より出力するパルスの位相差は、ジェネラルレジスタB(GRA)により設定します。

- (5) 本タスク例では、周期が16.25ms、位相差が3.125msのパルスを出力します。

図1 任意の位相差のパルス出力

### 使用機能説明

- (1) 本タスク例では、タイマWアウトプットコンペア機能を使用して、FTIOA、FTIOB出力端子より任意の 位相差のパルスを出力します。

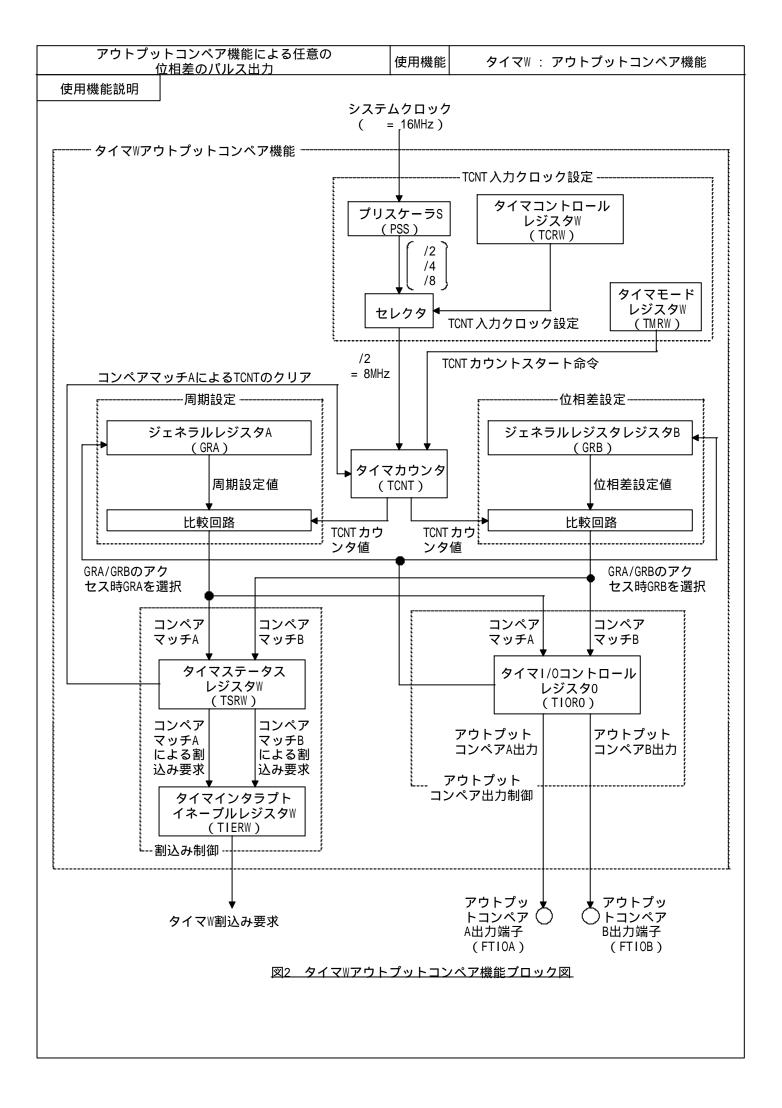

- (a)図2にタイマWアウトプットコンペア機能のブロック図を示します。以下にタイマWアウトプット コンペア機能のブロック図について説明します。

- ・システムクロック( )は、16MHzのOSCクロックで、CPUおよび周辺機能を動作させるための 基準クロックです。

- ・プリスケーラS(PSS)は、 を入力とする13ビットのカウンタで、1サイクルごとにカウント アップします。

- ・タイマカウンタ(TCNT)は、16ビットのリード/ライト可能なアップカウンタで、入力する内部 クロック/外部クロックによりカウントアップされます。入力するクロックは、システムクロッ クの2分周、4分周、8分周および外部クロックの計4種類のクロックより選択可能です。本タスク 例では、TCNTの入力クロックにシステムクロックの2分周のクロックを選択しています。

- ・タイマコントロールレジスタW(TCRW)は、8ビットのリード/ライト可能なレジスタで、TCNTの 入力クロックの選択を行ないます。

- ・タイマステータスレジスタW(TSRW)は、8ビットのレジスタで、カウンタクリアの選択、各割 込み要求信号の制御を行ないます。

- ・タイマインタラプトイネーブルレジスタW(TIERW)は、8ビットのリード/ライト可能なレジスタ で、各割込み要求の許可/禁止を制御します。

- ・タイマモードレジスタW(TMRW)は TCNTのカウンタスタート命令を行います。

- ・タイマI/0コントロールレジスタ0(TIORO)は、8ビットのリード/ライト可能なレジスタで、ア ウトプットコンペアレジスタの設定およびアウトプットコンペア出力の設定を行います。

- ・ジェネラルレジスタA (GRA)は、16ビットのリード/ライト可能なレジスタで、 GRAの内容はTCNTと常に比較されており、両者の値が一致すると、TSRWのIMFAが"1"にセット されます。この時、TIERWのIMIEAが"1"ならばCPUに割込みを要求します。また、コンペアマッ チAが発生したとき、TIOROのIOA2が"0"にセットされていると、TIOROのIOA1、IOA0で設定したレ ベル値がFTIOA端子に出力されます。

- ・ジェネラルレジスタレジスタB ( GRB ) は、16ビットのリード/ライト可能なレジスタで、 GRBの内容はTCNTと常に比較されており、両者の値が一致すると、TSRWのIMFBが"1"にセット されます。この時、TIERWのIMIEBが"1"ならばCPUに割込みを要求します。また、コンペアマッ チBが発生したとき、TIOROのIOB2が"0"にセットされていると、TIOROのIOB1、IOBOで設定したレ ベル値がFTIOB端子に出力されます。

- ・アウトプットコンペアA出力端子(FTIOA)より、コンペアマッチAによるパルスを出力します。 ・アウトプットコンペアB出力端子(FTIOB)より、コンペアマッチBによるパルスを出力します。

| アウトプットコンペア機能による任意の |

|--------------------|

| 位相差のパルス出力          |

タイマW: アウトプットコンペア機能

## 使用機能説明

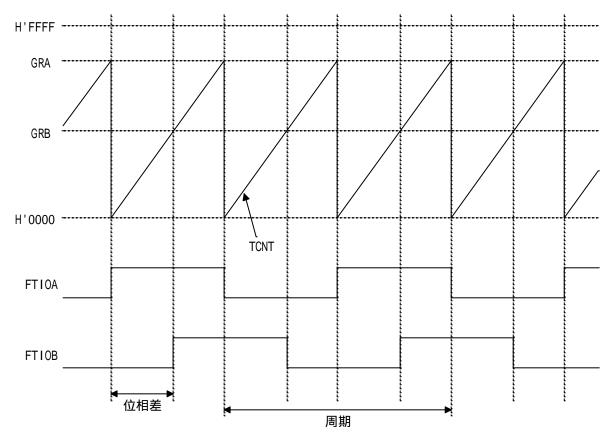

(b) 図3に出力パルスの周期、および位相差の設定方法について示します。

周期 = 2 × GRA × TCNT入力クロック周期

= 2 × GRA × 0.125 µ s(プリスケーラჽ:2 × システムクロック:62.5ns) 位相差 = GRB × TCNT入力クロック周期

= GRB × 0.125 µ s(プ リスケーラS:2 × システムクロック:62.5ns)

図3 出力パルスの周期、および位相差の設定方法

(2)表1に本タスク例の機能割付けを示します。表1に示すように機能を割付け、タイマWアウトプット コンペア機能による任意の位相差のパルス出力を行ないます。

表1 機能割付け

| 機能    | 機能割付け                                                    |  |

|-------|----------------------------------------------------------|--|

| PSS   | システムクロックを入力とする13ビットのカウンタ                                 |  |

| TIERW | コンペアマッチA、コンペアマッチBによる割込みの許可を設定                            |  |

| TSRW  | コンペアマッチA、コンペアマッチBによる割込み要求信号の制御、コンペアマッチAによるTCNTのクリアの許可を設定 |  |

| TCNT  | システムクロックを2分周したクロックを入力とする16ビットのアップカウンタ                    |  |

| GRA   | 出力パルスの周期を設定、TCNTのカウンタ値と一致するとコンペアマッチAが発生                  |  |

| GRB   | 出力パルスの位相差を設定、TCNTのカウンタ値と一致するとコンペアマッチBが発生                 |  |

| TCRW  | TCNT 入力クロックの設定                                           |  |

| TMRW  | TCNTカウントスタート設定                                           |  |

| TIORO | アウトプットコンペアレジスタの設定、アウトプットコンペア出力の設定                        |  |

| FTIOA | コンペアマッチAによるパルスの出力端子                                      |  |

| FTIOB | コンペアマッチBによるパルスの出力端子                                      |  |

タイマW: アウトプットコンペア機能

## 動作原理

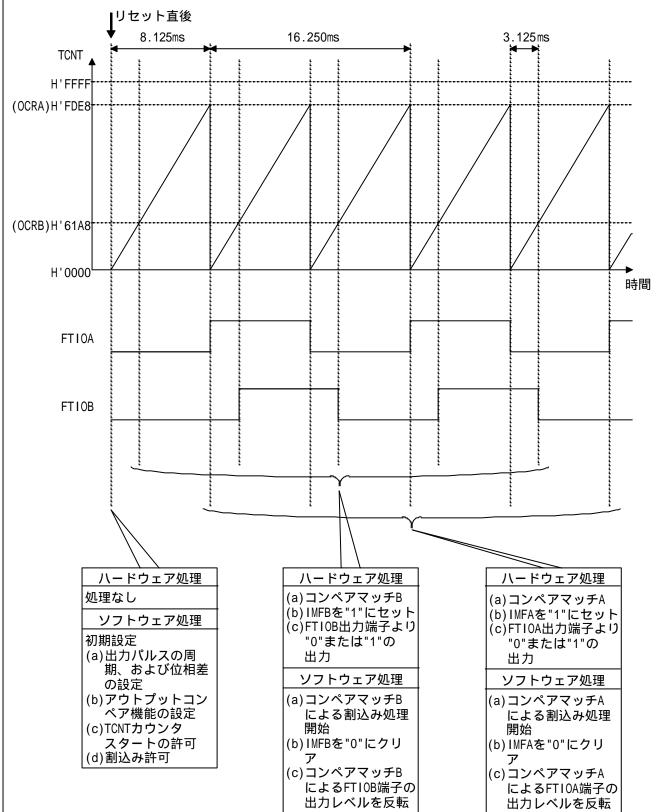

(1)図4に動作原理を示します。図3に示すようなハードウェア処理、およびソフトウェア処理によりタイマWアウトプットコンペア機能による任意の位相差のパルス出力を行ないます。

図4 タイマWアウトプットコンペア機能による任意の位相差のパルス出力の動作原理

## ソフトウェア説明

## (1) モジュール説明

表2に本タスク例におけるモジュール説明を示します。

## 表2 モジュール説明

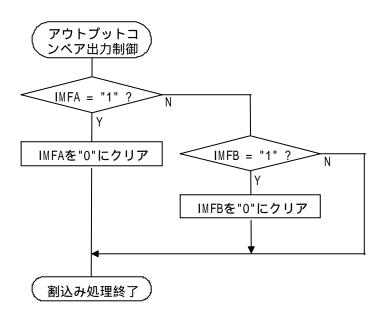

| モジュール名             | ラベル名  | 機能                                                                                  |  |

|--------------------|-------|-------------------------------------------------------------------------------------|--|

| メインルーチン            | main  | コンペアマッチ機能の設定、割込みの許可を行なう                                                             |  |

| アウトプットコン<br>ペア出力制御 | twint | タイマW割込み処理ルーチンで、IMFAによる割込み要求かIMFBによる<br>割込み要求かを判定し、FTIOA、またはFTIOB端子の出力レベルを反転<br>を行なう |  |

#### (2)引数の説明

本タスク例では、引数は使用していません。

## (3)使用内部レジスタ説明

表3に本タスク例における使用内部レジスタ説明を示します。

## 表3 使用内部レジスタ説明

| レジスタ名 |                      | 機能                                                                                                                                                            | アドレス                           | 設定値                              |

|-------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------|

| TMRW  | CTS                  | タイマモードスレジスタW<br>(タイマカウンタスタート)<br>: CTS="1"のとき、TCNTがカウンタ開始を示す<br>: CTS="0"のとき、TCNTがカウンタ停止を示す                                                                   | H'FF80<br>ビット7                 | 1                                |

| TCRW  | CCLR                 | タイマコントロールレジスタW<br>(カウンタクリア)<br>:CCLR="1"のとき、コンペアマッチAによるTCNTのクリアを許可                                                                                            | H'FF81<br>ビット7                 | 1                                |

|       | CKS2<br>CKS1<br>CKS0 | タイマコントロールレジスタW(クロックセレクト1、0)<br>: CKS2="0"、CKS1="0"、CKS0="1"のとき、TCNTの入力クロック<br>をシステムクロックの2分周のクロックに設定                                                           | H'FF81<br>ビット6<br>ビット5<br>ビット4 | CKS2="0"<br>CKS1="0"<br>CKS0="1" |

|       | ТОВ                  | タイマコントロールレジスタW(タイマ出力レベルセットB)<br>: TOB="1"のとき、コンペアマッチBが発生するまで、FTIOB端子<br>に出力するレベルを"High"レベルに設定<br>: TOB="0"のとき、コンペアマッチBが発生するまで、FTIOB端子<br>に出力するレベルを"Low"レベルに設定 | H'FF81<br>ビット1                 | 0                                |

|       | TOA                  | タイマコントロールレジスタW(タイマ出力レベルセットA)<br>: TOA="1"のとき、コンペアマッチAが発生するまで、FTIOA端子<br>に出力するレベルを"High"レベルに設定<br>: TOA="0"のとき、コンペアマッチAが発生するまで、FTIOA端子<br>に出力するレベルを"Low"レベルに設定 | H'FF81<br>ビット0                 | 0                                |

| TIERW | IMIEB                | タイマインタラプトイネーブルレジスタW<br>(アウトプットコンペア割込みBイネーブル)<br>:IMIEB="1"のとき、IMFBによる割込みを許可                                                                                   | H'FF82<br>ビット1                 | 1                                |

|       | IMIEA                | タイマインタラプトイネーブルレジスタW<br>(アウトプットコンペア割込みAイネーブル)<br>: IMIEA="1"のとき、IMFAによる割込みを許可                                                                                  | H'FF82<br>ビット0                 | 1                                |

| TSRW  | IMFB                 | タイマステータスレジスタW<br>(アウトプットコンペアフラグB)<br>:IMFB="0"のとき、TCNTとGRBがコンペアマッチしていないこ<br>とを示す<br>:IMFB="1"のとき、TCNTとGRBがコンペアマッチしたことを示す                                      | H'FF83<br>ビット1                 | 0                                |

|       | IMFA                 | タイマステータスレジスタW<br>(アウトプットコンペアフラグA)<br>:IMFA="0"のとき、TCNTとGRAがコンペアマッチしていないこ<br>とを示す<br>:IMFA="1"のとき、TCNTとGRAがコンペアマッチしたことを示す                                      | H'FF83<br>ビット0                 | 0                                |

タイマW: アウトプットコンペア機能

# ソフトウェア説明

# 表3 使用内部レジスタ説明

| レジスタ名     |              | 機能                                                                                                                                           | アドレス                   | 設定値                  |

|-----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------|

| TIORO     | 10B2         | タイマ1/0コントロールレジスタ0<br>(1/0コントロールB2)<br>:10B2="0"のとき、アウトプットコンペアBとして機能                                                                          | H'FF84<br>ビット6         | 0                    |

|           | IOB1<br>IOB0 | タイマI/0コントロールレジスタ0<br>(I/0コントロールB1~0)<br>: IOB1="1"のとき、コンペアマッチBにより、FTIOB端子出力を<br>トルグ出力に設定<br>: IOBO="1"のとき、コンペアマッチBにより、FTIOB端子出力を<br>トルグ出力に設定 | H'FF84<br>ビット5<br>ビット4 | IOB1="1"<br>IOB0="1" |

|           | 10 A2        | タイマ1/0コントロールレジスタ0<br>(1/0コントロールA2)<br>:10A2="0"のとき、アウトプットコンペアAとして機能                                                                          | H'FF84<br>ビット2         | 0                    |

|           | 10A1<br>10A0 | タイマI/0コントロールレジスタ0<br>(I/0コントロールA1~0)<br>: IOA1="1"のとき、コンペアマッチAにより、FTIOA端子出力を<br>トルグ出力に設定<br>: IOAO="1"のとき、コンペアマッチAにより、FTIOA端子出力を<br>トルグ出力に設定 | H'FF84<br>ビット1<br>ビット0 | IOA1="1"<br>IOA0="1" |

| TC        | ONT          | タイマカウンタ<br>:システムクロックの2分周のクロックを入力とする16ビット<br>のアップカウンタ                                                                                         | H'FF86                 | H'7530               |

| GRA       |              | ジェネラルレジスタA<br>: GRAの設定値とTCNTのカウンタ値が一致すると、コンペア<br>マッチAが発生                                                                                     | H'FF88                 | H'FDE8               |

| GRB : GRB |              | ジェネラルレジスタB<br>:GRBの設定値とTCNTのカウンタ値が一致すると、コンペア<br>マッチBが発生                                                                                      | H'FF8A                 | H'61A8               |

## (4)使用RAM説明

本タスク例では、RAMは使用しません。

#### フローチャート

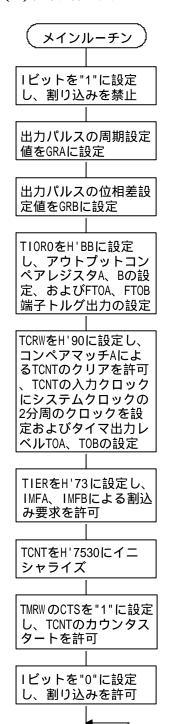

#### (a)メインルーチン

#### (b) タイマW割込み処理ルーチン

本例ではスタックポインタはINIT.SRC(アセンブリ言語)で 設定してあります。

タイマW: アウトプットコンペア機能

### プログラムリスト

```

INIT.SRC(プログラムリスト)

```

```

.EXPORT _INIT

.IMPORT _main

;

.SECTION P,CODE

_INIT:

MOV.W #H'FF80,R7

LDC.B #B'10000000,CCR

JMP @_main

;

.END

```

```

/*

H8/300H Tiny Series -H8/3664-

Application Note

'Pulse Output of Random Phase Difference by

Output Compare Function'

Function.

: Timer W Output Compare

External Clock: 16MHz

Internal Clock : 16MHz

/*

Sub Clock : 32.768kHz

/*

#include <machine.h>

Symbol Defnition

struct BIT {

unsigned char b7:1; unsigned char b6:1;

/* bit7 */

/* bit6 */

/* bit5 */

unsigned char b5:1;

/* bit4 */

unsigned char b4:1;

/* bit3 */

unsigned char

b3:1;

/* bit2 */

unsigned char

b2:1;

/* bit1 */

unsigned char b1:1;

/* bit0 */

unsigned char

b0:1;

};

TMRW

*(volatile unsigned char *)0xFF80 /* Timer Mode

#define

Register W

*(volatile unsigned char *)0xFF81 /* Timer Control Register W

#define

TCRW

(*(struct BIT *)0xFF81)

/* Timer Control Register W

#define

TCRW_BIT

/* Counter Clear A

#define

CCLR

TCRW_BIT.b7

/* Clock Select 1

#define

CKS1

TCRW_BIT.b5

/* Clock Select 0

#define

CKS0

TCRW BIT.b4

/* Timer Output Level B

#define

T0B

TCRW_BIT.b1

TOA

/* Timer Output Level A

#define

TCRW_BIT_b0

#define

TIERW

*(volatile unsigned char *)0xFF82

/* Timer Interrupt Enable Register

/* Timer Interrupt Enable Register

(*(struct BIT *)0xFF82)

#define

TIERW_BIT

/* Timer Overflow Interrupt Enable

#define

TIERW_BIT.b7

OVIE

/* Output Compare Interrupt B Enable */

#define

IMIFB

TIERW_BIT.b1

/* Output Compare Interrupt A Enable */

#define

IMIEA

TIERW_BIT.b0

/* Timer Status Register W

*(volatile unsigned char *)0xFF83

#define

TSRW

#define

(*(struct BIT *)0xFF83)

/* Timer Status Register W

TSRW_BIT

/* Timer Over flow

#define

OVF

TSRW_BIT.b7

/* Output Compare Flag B

#define

IMFB

TSRW_BIT.b1

#define

/* Output Compare Flag A

IMFA

TSRW_BIT.b0

/* Timer I/O Control Register 0

#define

*(volatile unsigned char *)0xFF84

TIORO

/* Timer I/O Control Register 0

TIORO_BIT

(*(struct BIT *)0xFF84)

#define

/* I/O Control Register B2

#define

10B2

TIORO_BIT.b6

/* I/O Control Register B1

#define

IOB1

TIORO_BIT.b5

/* I/O Control Register BO

#define

10B0

TIORO_BIT.b4

```

タイマW: アウトプットコンペア機能

## プログラムリスト

```

#define

10A2

TIORO_BIT.b2

/* I/O Control Register A2

/* I/O Control Register A1

IOA1

TIORO_BIT.b1

#define

/* I/O Control Register AO

#define

10A0

TIORO BIT.b0

/* Time Counter

*(volatile unsigned int *)0xFF86

#define

TCNT

*(volatile unsigned int *)0xFF88

/* General Register A

#define

GRA

*(volatile unsigned int *)0xFF8A

/* General Register B

#define

GRB

#pragma interrupt (twint)

/**********************************/

関数定義

void INIT ( void );

/* SP Set

extern

void

main

( void );

main ( void );

twint ( void );

void

/* Vector Address

#pragma section V1

/* VECTOR SECTOIN SET */

void (*const VEC_TBL1[])(void) = {

/* 0x00 - 0x0f */

INIT

/* 00 Reset

#pragma section V2

/* VECTOR SECTOIN SET */

void (*const VEC_TBL2[])(void) = {

twint

/* 2A Timer W Interrupt */

};

#pragma

section

Main Program

void main ( void )

set_imask_ccr(1);

/* Interrupt Disable

GRA = 0xFDE8;

/* Initialize GRA

/* Initialize GRB

GRB = 0x61A8;

/* Initialize Output Compare Function */

TIORO = 0xBB;

TCRW = 0x90;

/* Initialize TCNT Input Clock Period

/* Initialize IMIEA/IMIEB Interrupt Enable */

TIERW = 0x73;

TCNT = 0x7530;

/* Initialize TCNT

/* Initialize timer Mode Register

TMRW = 0xC8:

*/

set_imask_ccr(0);

/* Interrupt Enable

while(1) {

}

```

## アウトプットコンペア機能による任意の 位相差のパルス出力

使用機能

タイマW: アウトプットコンペア機能

# プログラムリスト

# リンクアドレス指定

| セクション名   | アドレス      |

|----------|-----------|

| 277 17 1 | 7 1 7 1 1 |

| CV1      | H'0000    |

| CV2      | H'002A    |

| Р        | H'0100    |