クロック同期式シリアルデータ受信

使用機能

SCI3 : クロック同期式シリアル転送機能

#### 仕様

- (1)図1に示すようにクロック同期式シリアル転送機能を使用して、4バイトの8ビットデータの受信を 行ないます。

- (2) 転送クロックは、外部クロックを使用します。

- (3) 受信するデータのデータ長は8ビットで、データの最下位ビットから受信するLSBファースト方式に よる受信を行います。

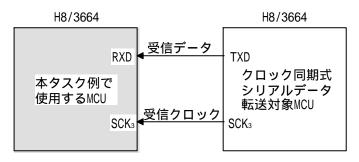

図1 クロック同期式シリアルデータ受信

#### 使用機能説明

- (1) 本タスク例では、シリアルコミュニケーションインタフェース (SCI: Serial Communication Interface)を 使用して、クロック同期式のシリアルデータの受信を行ないます。図2にクロック同期式シリアルデータ受信 のブロック図を示します。以下にクロック同期式シリアルデータ受信のブロック図について説明します。。

- ・受信エラーの検出には、オーバランエラーのみを行います。

- ・クロック同期式モードではデータ長は8ビットになります。

- ・レシーブシフトレジスタ(RSR)は、シリアルデータを受信するためのレジスタです。RSRにRXD端子から 入力されたシリアルデータを、LSB (ビット0)から受信した順にセットしパラレルデータに変換します。 1バイトのデータを受信すると、データは自動的にRDRへ転送されます。CPUからRSRを直接リード/ライト することはできません。

- ・レシーブデータレジスタ(RDR)は、受信したシリアルデータを格納する8ビットのレジスタです。1バイ トのデータの受信が終了すると、受信したデータをRSRからRDRへ転送し、受信動作を完了します。その後 、RSRは受信可能となります。RSRとRDRはダブルバッファになっているため連続した受信動作が可能で す。RDRは受信専用レジスタなのでCPUからライトできません。

- ・トランスミットシフトレジスタ (TSR) は、シリアルデータを送信するためのレジスタです。TDRから送 信データをいったんTSRに転送し、LSB (ビット0)から順にTXD端子に送出することでシリアルデータ送 信を行ないます。1バイトのデータを送信すると、自動的にTDRからTSRへ次の送信データを転送し、送信

- 信を行ないます。1八イトのテータを送信すると、自動的にTDRからTSRへ次の送信テータを転送し、送信を開始します。ただし、TDRにデータが書き込まれていない(TDREに"1"がセットされている)場合にはTDRからTSRへのデータ転送は行ないません。CPUからTSRを直接リード/ライトすることはできません。・トランスミットデータレジスタ(TDR)は、送信データを格納する8ビットのレジスタです。TSRの"空"を検出すると、TDRに書き込まれた送信データをTSRに転送し、シリアルデータ送信を開始します。TSRのシリアルデータ送信中に、TDRに次の送信データをライトしておくと、連続送信が可能です。TDRは、常にCPUによるリード/ライトが可能です。・シリアルモードレジスタ(SMR)は、シリアルデータ通信フォーマットの設定と、内蔵ボーレートジェネレータのクロックソースを選択するための8ビットのレジスタです。・シリアルコントロールレジスタ(SCR2)は、芸信/受信和作者とび送信/受信クロックソースの選択を

- ・シリアルコントロールレジスタ3(SCR3)は、送信/受信動作および送信/受信クロックソース の選択を 行なう8ビットのレジスタです。

- ・シリアルステータスレジスタ(SSR)は、SCI3のステータスフラグと送受信マルチプロセッサビットで構 成されています。TDRE、RDRF、OER、PER、FERはクリアのみ可能です。

- ・転送クロックは、8種類の内部クロックと外部クロックから選択できます。内部クロックを選択した場合 は、SCK<sub>3</sub>端子は出力端子となります。クロック連続出力モードに設定すると選択したクロックをSCK<sub>3</sub>端子 から連続して出力します。外部クロックを選択した場合は、SCK3端子はクロック入力端子となります。

- ・本タスク例では、転送クロックソースを外部クロックに設定しています。

- ・SCI3の転送フォーマットは8ビットのデータを選択可能です。データの最下位ビットから送受信されるL SBファースト方式による転送を行ないます。送信データは、転送クロックの立ち下がりから次の立ち上 がりまで出力されます。また、受信データは転送クロックの立ち上がりで取り込まれます。

- ・本タスク例では、動作モードを8ビットモードに設定し、8ビットのデータ受信を行ないます。

- ・SCI3クロック(SCK3)は、SCI3のクロック入出力端子です。

- ・SCI3レシーブデータ入力(RXD)は、SCI3の受信データの入力端子です。

【注】(a)外部クロックを受信する。

(h)

データ出力端子 (TXD)

SCI3受信 データ入力端子 (RXD)

(b)シリアルデータ通信フォーマットの設定を行う。

割込み要求(TEI、TXI、RXI、ERI)

(c)送信/受信動作、クロック同期式モードでのクロック入力の選択を行う。

レシーブシフトレジスタ

(RSR)

(d)ステータスフラグ(レシーブデータレジスタフル、オーバランエラー)によりSCI3の動作状態を示す。

・受信データ制御・

(f)

レシーブデータレジスタ

(RDR)

- (e)TSRの"空"を検出することにより、TDRに書き込まれた送信データをTSRに転送。

- (f)1バイトのデータの受信が終了すると、受信したデータをRSRからRDRへ転送。

- (g)送信データを送信する。

- (h)受信データを受信する。

- (2)表1に本タスク例の機能割付け示します。表1に示すように機能を割り付け、クロック同期式シリアルデータ受信を行ないます。

表1 機能割付け

| 機能   | 機能割付け                                  |

|------|----------------------------------------|

| RSR  | シリアルデータを受信するためのレジスタ                    |

| RDR  | 受信データを格納するレジスタ                         |

| SMR  | シリアルデータ通信フォーマットの設定                     |

| SSR  | SCI3の動作状態を示すステータスフラグ                   |

| SCR3 | 受信動作、SCK <sub>3</sub> の端子機能をクロック入力端子設定 |

| SCK₃ | SCI3のクロック入力端子                          |

| RXD  | SCI3の受信データ入力端子                         |

## 動作原理

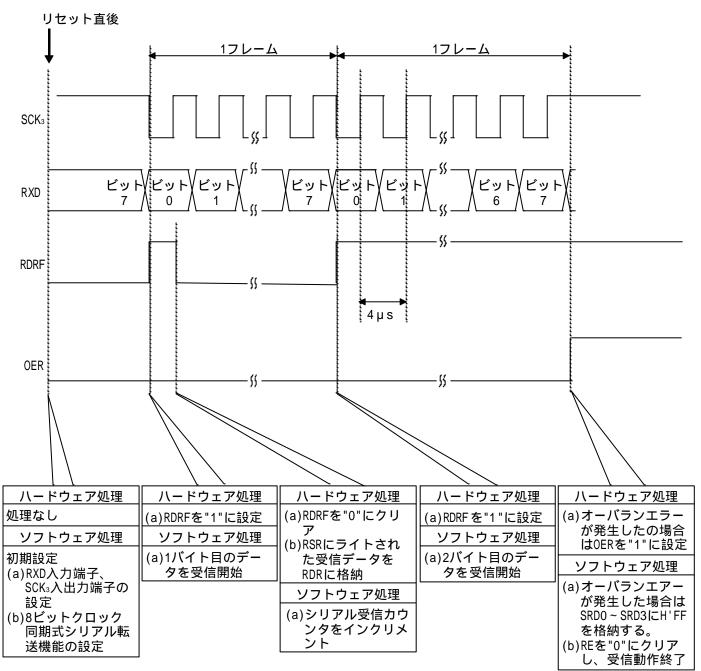

(1)図3に動作原理を示します。図3に示すようなハードウェア処理、およびソフトウェア処理によりクロック同期式シリアルデータ受信を行ないます。

図3 クロック同期式シリアル受信の動作原理

使用機能

SCI3 : クロック同期式シリアル転送機能

## ソフトウェア説明

# (1) モジュール説明

表2に本タスク例におけるモジュール説明を示します。

# 表2 モジュール説明

| モジュール名  | ラベル名 | 機能                                                                      |  |

|---------|------|-------------------------------------------------------------------------|--|

| メインルーチン |      | クロック同期式シリアルデータ受信の設定、受信エラーが発生した場合にはSRDO~SRD3に'HFFを格納、4バイトのデータを受信したところで終了 |  |

## (2)引数の説明

表3に本タスク例で使用する引数を示します。

#### 表3 引数の説明

|   | 引数名         | 機能                        | 使用モジュール名 | データ長 | 入出力 |

|---|-------------|---------------------------|----------|------|-----|

| ĺ | SRD0 ~ SRD3 | RDO~SRD3 クロック同期式シリアル受信データ |          | 1バイト | 入力  |

## (3)使用内部レジスタ説明

表4に本タスク例における使用内部レジスタ説明を示します。

## 表4 使用内部レジスタ説明

| レジスタ名 |              | 機能                                                                                                                  | アドレス                   | 設定値                   |

|-------|--------------|---------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|

| SMR   | COM          | シリアルモードレジスタ (コミュニケーションモード)<br>: COM="1"のとき、コミュニケーションモードをクロック同期<br>式モードに設定                                           | H'FFA8<br>ビット7         | 1                     |

|       | MP           | シリアルモードレジスタ(マルチプロセッサモード)<br>: MP="0"のとき、マルチプロセッサ通信機能を禁止                                                             | H'FFA8<br>ビット2         | 0                     |

|       | RE           | シリアルコントロールレジスタ3<br>(レシーブイネーブル)<br>: RE="1"のとき、受信動作を許可                                                               | H'FFAA<br>ビット4         | 1                     |

| SCR3  | CKE1<br>CKE0 | シリアルコントロールレジスタ3<br>(クロックイネーブル1、0)<br>: CKE1="1"、CKE0="0"のとき、クロック同期式モードにおいて<br>クロックソースを外部クロック、SCK₃端子機能をクロック入<br>力に設定 | H'FFAA<br>ビット1<br>ビット0 | CKE1="1 "<br>CKE0="0" |

| RI    | OR           | レシーブデータレジスタ<br>: 受信データを格納する8ビットのレジスタ                                                                                | H'FFAD                 | -                     |

| 000   | RDRF         | シリアルステータスレジスタ(レシーブデータレジスタフル)<br>:RDRF="0"のとき、RDRに受信データが格納されていない。<br>:RDRF="1"のとき、RDRに受信データが格納されている。                 | H'FFAC<br>ビット6         | 1                     |

| SSR   | OER          | シリアルステータスレジスタ(オーバランエラー)<br>: OER="0"のとき、受信中、または受信を完了<br>: OER="1"のとき、受信時にオーバランエラーが発生                                | H'FFAC<br>ビット5         | 0                     |

## (4)使用RAM説明

表5に本タスク例における使用RAM説明を示します。

表5 使用RAM説明

| ラベル名    | 機能                                  | アドレス   | 使用モジュール名 |

|---------|-------------------------------------|--------|----------|

| SRDO    | クロック同期式シリアル受信データの1バイト目を格納           | H'FB80 | メインルーチン  |

| SRD1    | クロック同期式シリアル受信データの2バイト目を格納           | H'FB81 | メインルーチン  |

| SRD2    | クロック同期式シリアル受信データの3バイト目を格納           | H'FB82 | メインルーチン  |

| SRD3    | クロック同期式シリアル受信データの4バイト目を格納           | H'FB83 | メインルーチン  |

| counter | クロック同期式シリアル受信動作を4カウントする8<br>ビットカウンタ | H'FB84 | メインルーチン  |

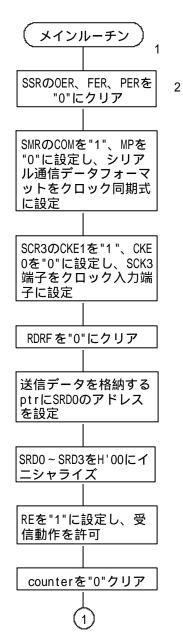

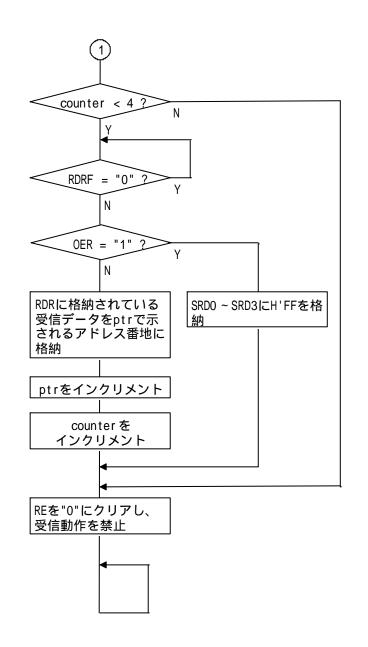

#### フローチャート

#### (a) メインルーチン

1:本例ではスタックポインタはINIT.SRC(アセンブリ言語)で 設定してあります。

2: クロック同期式(受信)ではOER、FER、PERを"0"クリアにしておく必要がある。

## プログラムリスト

```

INIT.SRC(プログラムリスト)

```

```

.EXPORT _INIT

.IMPORT _main

;

.SECTION P,CODE

_INIT:

MOV.W #H'FF80,R7

LDC.B #B'10000000,CCR

JMP @_main

;

.END

```

```

H8/300H Tiny Series -H8/3664-

Application Note

/*

/*

'Synchronous Serial Data Receotion'

/*

Funct ion

: Serial Communication Interface

/*

Synchronous Serial Interface

-Receiving

/*

External Clock: 16MHz

/*

Internal Clock : 16MHz

Sub Clock : 32.768kHz

/*

****************

#include <machine.h>

/* Symbol Defnition

struct BIT {

unsigned char b7:1; /* bit7 */

unsigned char b6:1; /* bit6 */

unsigned char b5:1; /* bit5 */

unsigned char b4:1; /* bit4 */

unsigned char b3:1; /* bit3 */

unsigned char b2:1; /* bit2 */

/* bit1 */

/* bit0 */

unsigned char b1:1;

unsigned char b0:1;

};

/* Serial Mode Register

#define SMR_BIT (*(struct BIT *)0xFFA8)

#define COM SMR_BIT.b7

#define MP SMR_BIT.b2

#define SCR3_BIT (*(struct BIT *)0xFFAA)

/* Communication Mode

/* Multiprocesor Mode

/* Serial Control Register 3 */

#define RE SCR3_BIT.b4

#define CKE1 SCR3_BIT.b1

#define CKE0 SCR3_BIT.b0

/* Receive Enable

#define CKE1 SCR3_BIT.b1

#define CKE0 SCR3_BIT.b0

#define SSR_BIT (*(struct BIT *)0xFFAC)

/* Clock Enable 1

/* Clock Enable 0

/* Serial Status Register

#define RDRF SSR_BIT.b6 /* Receive Data Register Full

#define OER SSR_BIT.b5 /* Overrun Erorr

#define FER SSR_BIT.b4 /* Framing Erorr

#define PER SSR_BIT.b3 /* Parity Erorr

#define RDR *(volatile unsigned char *)0xFFAD /* Receive data Register

/* Receive Data Register Full */

/* 関数定義

extern void INIT( void );

/* SP Set

void main (void);

```

#### プログラムリスト

```

/* RAM Allocation

unsigned char SRD[4]; unsigned char counter;

/* Vector Address */

#pragma section V1

/* VECTOR SECTOIN SET

*/

void (*const VEC_TBL1[])(void) = {

/* 0x00 - 0x0f */

INIT

/* 00 Reset

};

/* P

#pragma section

void main ( void )

{

unsigned char

*ptr;

OER = 0;

/* Clear OER

FER = 0;

/* Clear FER

*/

PER = 0;

/* Clear PER

COM = 1;

/* Initialize Communication Mode

/* Initialize Multiprocesor Mode

MP = 0;

*/

*/

/* Initialize Clock Enable 1

CKE1 = 1;

/* Initialize Clock Enable 0

*/

CKE0 = 0;

RDRF = 0;

/* Clear RDRF

ptr = \&SRD[0];

/* Initialize Serial Receiving Data Addreass */

SRD[0] = 0x00;

/* Initialize Serial Receiving Data 0

SRD[1] = 0x00;

/* Initialize Serial Receiving Data 1

*/

/* Initialize Serial Receiving Data 2

*/

SRD[2] = 0x00;

*/

/* Initialize Serial Receiving Data 3

SRD[3] = 0x00;

*/

/* Start Serial Receiving

RE = 1;

counter = 0;

/* Clear counter

while (counter < 4){

/* Serial Receiving Data Counter 4 Loop

while(RDRF == 0){

/* RDRF = 1 ?

*/

/* Overrun Erorr Flag = 1 ?

if (OER == 1){

/* Overrun Erorr 0

/* Overrun Erorr 1

SRD[0] = 0xFF;

*/

SRD[1] = 0xFF;

/* Overrun Erorr 2

SRD[2] = 0xFF;

/* Overrun Erorr 3

SRD[3] = 0xFF;

break;

else {

/* Save Serial Receiving Data

*ptr = RDR;

/* Increment Serial Receiving Data Address

/* Increment counter

ptr++;

counter++;

}

```

# プログラムリスト

# リンクアドレス指定

| セクション名 | アドレス   |

|--------|--------|

| CV1    | H'0000 |

| P      | H'0100 |

| B      | H'FB80 |